1. (a) Name the three major groups of contamination and briefly describe their physical characteristics.

(b) Where do the above contamination types come from? Give one example of each.

2. Name two processes metrics which would be worsened by poor cleanroom practices in a semiconductor cleanroom. Describe briefly what is meant by each term.

3. (a) What sizes of particles would cause problems for the following processes:

- 5 μm bipolar

- 4.5 μm NMOS

- 1.1 μm CMOS

- 0.9 μm BICMOS

- 0.3 μm CMOS?

(c) What effect is illustrated by the above?

(d) What additional particle related issue affects smaller feature size processes?

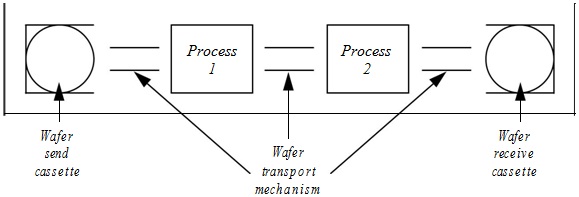

4. FIGURE 1 shows a system which is to be assessed for particles. The maximum specification limit on the system is +100 particles of >0.5 μm.

(a) A CWC is run by processing a test wafer through the entire sequence (process module 1 and module 2) and it reveals that 350 particles of >0.5 μm have been added. Comment on this finding.

(b) A second CWC is run with the wafer being processed only through module 1 and it reveals that 334 particles of >0.5 μm have been added. Comment on this finding.

(c) A third CWC is run with the wafer being processed through module 2 and it reveals that 328 particles of >0.5 μm have been added. Comment on this finding.

(d) Suggest where the particles may be coming from and suggest ways to isolate the sources of particles.

FIG. 1

5. The approximate number, N, of square chips of area A that can be formed on a wafer of diameter D is given by the equation:

N ≈ π/4A.(D - √A)2

A VLSI chip is to be fabricated on a 300 mm wafer and uses 6 lithography processes. It is reckoned that on average there will be 2 defects per wafer for each lithographic process. Assume the defects fall on different chips.

Calculate the cumulative percentage yield of the lithography processes if the chip has an area of:

(a) 0.5 cm2

(b) 1 cm2

(c) 2 cm2

(d) 4 cm2.

Comment on the results.